# *NAMIBIA UNIVERSITY*

OF SCIENCE AND TECHNOLOGY

## **FACULTY OF COMPUTING AND INFORMATICS**

DEPARTMENT OF CYBER SECURITY

| QUALIFICATION: BACHELOR OF COMPUTER SCIENCE, BACHELOR OF COMPUTER IN CYBE |                      |  |  |  |

|---------------------------------------------------------------------------|----------------------|--|--|--|

| SECURITY & BACHELOR OF INFORMATICS                                        |                      |  |  |  |

| QUALIFICATION CODE: 07BACS, 07BCCS & 07BAIF                               | LEVEL: 5             |  |  |  |

| COURSE: COMPUTER ORGANISATION AND ARCHITECTURE                            | COURSE CODE: COA511S |  |  |  |

| DATE: NOVEMBER 2024                                                       | PAPER: THEORY        |  |  |  |

| <b>DURATION:</b> 2 HOURS                                                  | MARKS: 100           |  |  |  |

| FIRST OPPORTUNITY EXAMINATION QUESTION PAPER |                          |  |  |  |  |

|----------------------------------------------|--------------------------|--|--|--|--|

| EXAMINER(S)                                  | MR. JULIUS SILAA         |  |  |  |  |

|                                              | MR. PHIUS SHAMBABI       |  |  |  |  |

|                                              | MR. ERICKY IIPUMBU       |  |  |  |  |

|                                              | MR. ANDREAS AMUKWA       |  |  |  |  |

|                                              | MS. JENNYPHAR KAVIKAIRUA |  |  |  |  |

|                                              | MS. HILLARY KWALA        |  |  |  |  |

|                                              | MR. ADRIAAN GOBLER       |  |  |  |  |

| MODERATOR:                                   | MR. SEBASTIAN MUKUMBIRA  |  |  |  |  |

## THIS QUESTION PAPER CONSISTS OF 5 PAGES

(Excluding this front page)

#### INSTRUCTIONS

- 1. Answer ALL the questions on the answer scripts.

- 2. Write clearly and neatly.

- 3. Number the answers clearly.

## PERMISSIBLE MATERIALS

1. Calculator.

## SECTION A [15 MARKS]: Each Question Weighs 1 Mark.

Indicate whether each of the following statements is True or False

- 1. Overflow can only occur if there is a carry. [True / False]

- 2. A sequence of hexadecimal digits can be thought of as representing an integer in base 2. [True / False]

- 3. The prefetch buffer is a memory cache located on the RAM chip. [True / False]

- 4. An interrupt is a hardware-generated signal to the processor. [True / False]

- 5. RAM must be provided with a constant power supply. [True / False]

- 6. The Instruction Set Architecture (ISA) defines the machine language instructions that a computer can follow. [True / False]

- 7. Memory swapping is a situation where none of the processes in memory are in the ready state. [True / False]

- 8. I/O channels are commonly seen on microcomputers, whereas I/O controllers are used on mainframes. [True / False]

- 9. Cache memory is a much faster memory than the register file. [True / False]

- 10. In any number, the rightmost digit is referred to as the most significant digit.

[True / False]

- 11. The Kernel is a special type of programming language used to provide instructions to the monitor. [True / False]

- 12. Interrupt is one of the five states for a process. [True / False]

- 13. The instruction set is the programmer's means of controlling the processor.

[True / False]

- 14. Memory references are faster than register references. [True / False]

- 15. Microprogramming eases the task of designing and implementing the control

Unit and provides support for the family concept. [True / False]

### SECTION B [15 MARKS]: Each Question Weighs 1 Mark.

Choose the correct for each of the following:

- 1. On an optical CD, what are the areas between the pits called?

- A. lands

B. sectors

C. cylinders

D. strips

|  | 2. | Which processor componer                                                 | t temporarily stores data and instructions waiting to be  |  |

|--|----|--------------------------------------------------------------------------|-----------------------------------------------------------|--|

|  |    | processed by the ALU?                                                    |                                                           |  |

|  |    | A. registers                                                             | B. CPU interconnection                                    |  |

|  |    | C. ALU                                                                   | D. system bus                                             |  |

|  | 3. | What is the hexadecimal equivalent of binary 10100101?                   |                                                           |  |

|  |    | A. 0                                                                     | B. 5                                                      |  |

|  |    | C. A5                                                                    | D. 10                                                     |  |

|  | 4. | Which operand evaluates to true if one or both of its operands are true? |                                                           |  |

|  |    | A. NOT                                                                   | B. AND                                                    |  |

|  |    | C. NAND                                                                  | D. OR                                                     |  |

|  | 5. | In floating-point arithmetic                                             | what is it called when a positive exponent surpasses the  |  |

|  |    | maximum allowed exponer                                                  | t?                                                        |  |

|  |    | A. exponent underflow                                                    | B. exponent overflow                                      |  |

|  |    | C. significand underflow                                                 | D. significand overflow                                   |  |

|  | 6. | What is implemented using combinational circuits?                        |                                                           |  |

|  |    | A. nano memory                                                           | B. random access memory                                   |  |

|  |    | C. read only memory                                                      | D. no memory                                              |  |

|  | 7. | Which of the following exis                                              | ts in one of two states and remains in that state without |  |

|  |    | input?                                                                   |                                                           |  |

|  |    | A. assert                                                                | B. complex PLD                                            |  |

|  |    | C. decoder                                                               | D. flip-flop                                              |  |

|  | 8. | What is used in digital circu                                            | its to manage signal and data routing?                    |  |

|  |    | A. multiplexers                                                          | B. program counters                                       |  |

|  |    | C. flip-flops                                                            | D. gates                                                  |  |

|  | 9. | What specifies the operation                                             | on to be carried out?                                     |  |

|  |    | A. source operand reference                                              | e B. opcode                                               |  |

|  |    | C. next instruction reference                                            | e D. processor register                                   |  |

|  | 10 | . In the ARM architecture, al                                            | instructions have a consistent format and are how many    |  |

|  |    | bits long?                                                               |                                                           |  |

|  |    | A. 8                                                                     | B. 16                                                     |  |

|  |    | C. 32                                                                    | D. 64                                                     |  |

|     | A. control unit                                                                     | B. ALU                                                         |            |  |  |

|-----|-------------------------------------------------------------------------------------|----------------------------------------------------------------|------------|--|--|

|     | C. shifter                                                                          | D. branch                                                      |            |  |  |

|     | 12. Where is the address of the next instruction to be fetched stored?              |                                                                |            |  |  |

|     | A. instruction register                                                             | B. memory address register                                     |            |  |  |

|     | C. memory buffer register                                                           | D. program counter                                             |            |  |  |

|     | 13. Which type of register can only store data and can't be used to calculate an    |                                                                |            |  |  |

|     | operand's address?                                                                  |                                                                |            |  |  |

|     | A. General purpose                                                                  | B. Data                                                        |            |  |  |

|     | C. Address                                                                          | D. Condition code                                              |            |  |  |

|     | 14. What is a dispatchable unit of work within a process that has its own processor |                                                                |            |  |  |

|     | context and stack data area?                                                        |                                                                |            |  |  |

|     | A. Process                                                                          | B. Process switch                                              |            |  |  |

|     | C. Thread                                                                           | D. Thread switch                                               |            |  |  |

|     | 15. What kind of architecture u                                                     | tilizes numerous, finely detailed pipelin                      | e stages?  |  |  |

|     | A. parallel                                                                         | B. supe- pipelined                                             |            |  |  |

|     | C. superscalar D. hybrid                                                            |                                                                |            |  |  |

|     |                                                                                     |                                                                |            |  |  |

|     |                                                                                     | T                                                              |            |  |  |

| SEC | TION C [70 MARKS]: Comprehe                                                         | ension questions.                                              |            |  |  |

| Qu  | estion 1                                                                            |                                                                | [16 Marks] |  |  |

| a)  | Outline one defining technology and at least one (1) characteristic of each comput  |                                                                |            |  |  |

|     | generation, from the first to th                                                    | e fourth.                                                      | (4 marks)  |  |  |

| b)  | List and briefly describe the fo                                                    | ist and briefly describe the four CPU key components (4 marks) |            |  |  |

| c)  | Data transfer between computer hardware, devices, and networks is facilitated by    |                                                                |            |  |  |

|     | information processing systems. Identify and discuss four distinct methods          |                                                                |            |  |  |

11. What manages the flow of data and instructions into and out of the processor?

computers use to handle input and output operations

(8 marks)

Question 2 [19 Marks]

a) Illustrate the relationship between a computer's memory size, its access speed, and the associated cost using a well-labelled diagram. (5 marks)

- b) Identify and briefly explain the purpose of four CPU registers crucial for instruction

execution. (8 marks)

- c) In computing, cache replacement policies are strategies used by software or hardware to decide which data to remove from a cache when it's full and new data needs to be added. Name and briefly explain three of these strategies.

Note: Cache replacement policies are different from cache mapping schemes (6 marks)

Question 3 [10 Marks]

- a) Compare and contrast CISC (Complex Instruction Set Computing) and RISC (Reduced Instruction Set Computing) architectures, highlighting at least three key differences between them. Discuss the advantages and disadvantages of each approach in terms of performance, complexity, and code size (6 marks)

- b) Two well-known laws, Moore's law (1965) and Amdahl's law (1967), influence computer performance. Explain these laws in your own words. (4 marks)

Question 4 [09 Marks]

A spying glass with hidden camera has 0.25 GB of memory. Suppose this memory is word addressable meaning that every word has its own unique address for accessing it.

- a) If each word in memory has its own address, how many total words can be stored

in its memory? (assume a standard word size).

- b) Imagine this memory is organized into blocks, where each block holds 32 words.How. many blocks would this memory have? (3 marks)

- c) How many lines of cache memory will be required to accommodate all blocks

main memory in (b) above by using the direct cache addressing scheme? (2 marks)

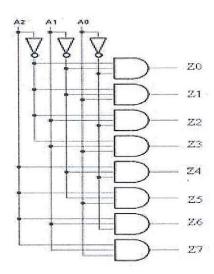

- a) Identify all sequential circuits from the following list

Decoder, Multiplexer, Flip flops (Latches), Comparator, Shift Registers,

PLA, ROM, Adder and, Encoder.

- b) Identify(name) the following important combinational circuit found in the CPU (2 marks)

c) Draw a truth table depicting the circuit above. Your truth table should include all input and output as shown in the diagram (10 marks)