# *NAMIBIA UNIVERSITY*

OF SCIENCE AND TECHNOLOGY

#### **FACULTY OF COMPUTING AND INFORMATICS**

DEPARTMENT OF COMPUTER SCIENCE

| QUALIFICATION: BACHELOR OF COMPUTER SCIENCE, BACHELOR OF COMPUTER IN CYBER |                      |  |

|----------------------------------------------------------------------------|----------------------|--|

| SECURITY & BACHELOR OF INFORMATICS                                         |                      |  |

| QUALIFICATION CODE: 07BACS, 07BCCS &                                       | LEVEL: 5             |  |

| 07BAIF                                                                     |                      |  |

| COURSE: COMPUTER ORGANISATION                                              | COURSE CODE: COA511S |  |

| AND ARCHITECTURE                                                           |                      |  |

| DATE: JANUARY 2025                                                         | PAPER: THEORY        |  |

|                                                                            |                      |  |

| <b>DURATION:</b> 2 HOURS                                                   | MARKS: 100           |  |

| SECOND OPPORTUNITY/SUPPLEMENTARY EXAMINATION QUESTION PAPER |                          |  |  |

|-------------------------------------------------------------|--------------------------|--|--|

| EXAMINER(S)                                                 | MR. JULIUS SILAA         |  |  |

|                                                             | MR. PHIUS SHAMBABI       |  |  |

| 6                                                           | MR. ERICKY IIPUMBU       |  |  |

|                                                             | MR. ANDREAS AMUKWA       |  |  |

|                                                             | MS. JENNYPHAR KAVIKAIRUA |  |  |

|                                                             | MS. HILLARY KWALA        |  |  |

|                                                             | MR. ADRIAAN GOBLER       |  |  |

| MODERATOR:                                                  | MR. SEBASTIAN MUKUMBIRA  |  |  |

## THIS QUESTION PAPER CONSISTS OF 5 PAGES

(Excluding this front page)

### **INSTRUCTIONS**

- 1. Answer ALL the questions on the answer scripts.

- 2. Write clearly and neatly.

- 3. Number the answers clearly.

#### PERMISSIBLE MATERIALS

1. Calculator.

#### SECTION A [15 MARKS]: Each Question Weighs 1 Mark.

Indicate whether each of the following statements is True or False.

- A microprocessor's speed is maximized when it receives a continuous stream of instructions without any interruptions. [True/False]

- In a pipelined processor, multiple instructions can be executed at the same time, each in different stages of completion. [True/False]

- The simplified instruction set of RISC processors allows for faster interrupt handling compared to CISC processors. [True/False]

- 4. Machine parallelism refers to the simultaneous execution of independent instructions, which can enhance overall performance. [True/False]

- Organizational attributes, such as the hardware design of a computer, are typically hidden from the programmer and do not affect how the programmer writes code. [True/False]

- 6. The Instruction Set Architecture (ISA) defines the set of instructions a processor can execute and determines how software interacts with hardware. [True/False]

- 7. Cache memory is generally faster than the register file because it is closer to the processor core. [True/False]

- 8. Overflow in arithmetic operations can occur without a carry, depending on the type of operation and how data is represented. [True/False]

- 9. The typical states of a process include: new, ready, running, waiting, and terminated, while interrupt handling is a separate mechanism. [True/False]

- 10. Memory swapping occurs when a process is moved to secondary storage to free up main memory for other processes. [True/False]

- 11. A hexadecimal digit represents 4 bits, and sequences of hexadecimal digits are often used to represent binary numbers in a more compact form. [True/False]

- 12. The instruction set of a processor allows the programmer to directly control the operations the processor performs. [True/False]

- 13. Memory references are typically faster than register references because memory can store more data than registers. [True/False]

- 14. The kernel is the core of the operating system, and it is typically written in low-level programming languages like C or assembly. [True/False]

15. A processor's clock frequency, measured in Hertz (Hz), directly affects how many instructions it can execute per second, influencing its performance. [True/False]

# SECTION B [15 MARKS]: Each Question Weighs 1 Mark.

Choose the correct answer for each of the following:

| 1. | Binary 11001010 is hexadecimal                                             |                                                        |  |

|----|----------------------------------------------------------------------------|--------------------------------------------------------|--|

|    | A. C A                                                                     | B. 9 A                                                 |  |

|    | C. D 2                                                                     | D. 6 A                                                 |  |

| 2. | can store data indefinitely until an input changes its state.              |                                                        |  |

|    | A. flip-flop                                                               | B. decoder                                             |  |

|    | C. multiplexer                                                             | D. latch                                               |  |

| 3. | The operand yields to                                                      | rue only if both of its operands are true.             |  |

|    | A. NOT                                                                     | B. AND                                                 |  |

|    | C. XOR                                                                     | D. OR                                                  |  |

| 4. | A is a part of a proces                                                    | ss that can execute independently and can have its own |  |

|    | execution context.                                                         |                                                        |  |

|    | A. process                                                                 | B. thread                                              |  |

|    | C. task                                                                    | D. process manager                                     |  |

| 5. | 5. In modern ARM architecture, the standard instruction size is bits lo    |                                                        |  |

|    | A. 8                                                                       | B. 16                                                  |  |

|    | C. 32                                                                      | D. 64                                                  |  |

| 6. | i. The is responsible for fetching instructions and decoding them in the C |                                                        |  |

|    | A. registers                                                               | B. control unit                                        |  |

|    | C. ALU                                                                     | D. system bus                                          |  |

| 7. | In digital circuits, are                                                   | used to select one out of multiple inputs based on a   |  |

|    | selection signal.                                                          |                                                        |  |

|    | A. multiplexers                                                            | B. counters                                            |  |

|    | C. flip-flops                                                              | D. encoders                                            |  |

| 8. | The identifies the loc                                                     | ation of the operand.                                  |  |

|    | A. opcode                                                                  | B. address register                                    |  |

|    | C. source operand                                                          | D. data register                                       |  |

| 9.                                                                                      | The operand can yield                | d true if at least one of its operands is tr | ue.               |

|-----------------------------------------------------------------------------------------|--------------------------------------|----------------------------------------------|-------------------|

|                                                                                         | A. AND                               | B. OR                                        |                   |

|                                                                                         | C. XOR                               | D. NOT                                       |                   |

| 10.                                                                                     | A architecture is desi               | gned to use multiple instruction pipeline    | es for parallel   |

|                                                                                         | processing of instructions.          |                                              |                   |

|                                                                                         | A. superscalar                       | B. scalar                                    |                   |

|                                                                                         | C. hybrid                            | D. super-pipelined                           |                   |

| 11                                                                                      | . The holds the next in              | struction to be executed in a sequence.      |                   |

|                                                                                         |                                      | B. memory address register                   |                   |

|                                                                                         | C. memory buffer register            | D. program counter                           |                   |

| 12                                                                                      |                                      | en the exponent falls below the minimur      | n possible        |

|                                                                                         | exponent, it is called               |                                              |                   |

|                                                                                         | A. significand underflow             | B. exponent underflow                        |                   |

|                                                                                         | C. significand overflow              | D. exponent overflow                         |                   |

| 13 registers are specialized for holding addresses used in memory operations.           |                                      |                                              |                   |

|                                                                                         | A. general purpose                   | B. address                                   |                   |

|                                                                                         | C. status                            | D. Control                                   |                   |

| 14                                                                                      | . In an optical CD, the areas that s | store data in the form of pits are called _  | ·                 |

|                                                                                         | A. lands                             | B. zones                                     |                   |

|                                                                                         | C. sectors                           | D. tracks                                    |                   |

| 15                                                                                      | . The manages the exc                | ecution of instructions by directing data    | and control       |

|                                                                                         | signals throughout the system.       |                                              |                   |

|                                                                                         | A. control unit                      | B. CPU interconnect                          |                   |

|                                                                                         | C. ALU                               | D. data path                                 |                   |

|                                                                                         |                                      |                                              |                   |

|                                                                                         |                                      |                                              |                   |

| SE                                                                                      | CTION C [70 MARKS]: Comprehe         | nsion questions.                             |                   |

| Q                                                                                       | uestion 1                            |                                              | [15 Marks]        |

| A new model of Raspberry Pi Phone has 32GB of RAM. The memory in this device is divided |                                      |                                              | device is divided |

| into several words, each consisting of 2048 bytes.                                      |                                      |                                              |                   |

| a) How many bits are needed to address any single word in this memory?                  |                                      |                                              |                   |

|                                                                                         | Show your work sten by sten          |                                              | (9 marks)         |

b) CPU is a vital computer resource and any good computing system should be design in such way to utilise CPU efficiently. Contrast programmed I/O from I/O channel.

Why the CPU usage by I/O channel CPU is more efficient than Programmed I/O?

(6 marks)

#### Question 2

[08 Marks]

a) Explain your understanding of the following virtual memory concepts

(4 marks)

- i) swapping

- ii) demand paging

- b) What is the ultimate importance of virtual memory management scheme? (4 marks)

#### Question 3

[14 Marks]

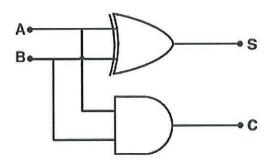

The following diagram represents a logical circuit. Please provide answers to the accompanying questions based on your understanding of circuit analysis

a) Provide the name of this circuit

(2 marks)

- b) Within the architecture of a CPU, where exactly would you find this circuit? (2 marks)

- c) Citing its components A, B, S and C, describe how this circuit work

(4 marks)

d) Let's say you want to design a circuit that turns on a light (output F) when the two switch inputs A and B are applied.

Truth Table

| A | В | F |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

- i. Provide a canonical Boolean function (F) for the circuit above (2 marks)

- ii. Suppose this Function does not require any further minimization. Create a visual representation(circuit) of this Boolean function using logic gates (4 marks)

Question 4 [10 Marks]

- a) Instructions need specific information to execute. Identify four places within a computer where the data used by an instruction (operands) can be located (4 marks)

- b) Provide an example of a low-level computer instruction and briefly describe what this instruction must specify. (6 marks)

Question 5 [12 Marks]

Addressing modes specify how an instruction finds its operand. Explain this with examples of:

a) Implicit addressing mode (3 marks)

b) Register Indirect addressing mode (3 marks)

c) Relative addressing mode (6 marks)

Question 6 [11 Marks]

- a) Imagine opening Facebook on your phone. Behind the scenes, your phone's CPU follows

a series of steps to make this happen. Explain the six stages the CPU goes through to

process the instructions that allow you to use the app. (6 marks)

- b) The Program Status Word (PSW) holds key information about a program's current state.

Name and briefly explain five common status flags found within a PSW. (5 marks)

\*\*\*\*\*END OF PAPER\*\*\*\*