|

COA511S - COMPUTER ORGANISATION AND ARCHITECTURE - 1ST OPP - NOV 2025 |

|

1 Page 1 |

▲back to top |

n Am I BI A u n IVER s I TY

OF SCIEnCE Ano TECHnOLOGY

FACULTY OF COMPUTING AND INFORMATICS

DEPARTMENT OF CYBER SECURITY

QUALIFICATION: BACHELOR OF COMPUTER SCIENCE, BACHELOR OF COMPUTER IN CYBER

SECURITY & BACHELOR OF INFORMATICS

QUALIFICATION CODE: 07BACS, 07BCCS &

07BAIF

LEVEL: 5

COURSE: COMPUTER ORGAN ISATION

AND ARCHITECTURE

COURSE CODE: COA511S

DATE: NOVEMBER 2025

PAPER: THEORY

DURATION: 2H

MARKS: 100

EXAMINER(S)

MODERATOR:

FIRST OPPORTUNITY EXAMINATION QUESTION PAPER

MR. JULIUS SILAA

MR. MBAUNGURAIJE TJUl<UZU

MR. PETRUS l<ATAMBO

MR. IMMANUEL NAM PALA

MR JACKSON NGHIDU Lll<A

MS. SEPISO CHll(URUWO

MR. ANDREAS AMUl<WA

DR . SEBASTIAN MUKUMBIRA

THIS QUESTION PAPER CONSISTS OF 6 PAGES

(Exclud ing t his front page)

INSTRUCTIONS

1. Answer ALL the questions on the answer scripts.

2. Write clearly and neatly.

3. Number the answers clearly.

PERMISSIBLE MATERIALS

1. None.

|

2 Page 2 |

▲back to top |

SECTION A (15 MARKS): Each Question Weighs 1 Mark.

Indicate whether each of the following statements is True or False

1. The Direct Memory Access (OMA) technique allows the 1/0 module and main memory to

transfer data directly, without processor involvement. True/ False

2. The binary system, while convenient for computers, is extremely cumbersome for humans.

True/ False

3. SRAM is used as the building block for level 1 cache memory in computer systems.

True/ False

4. Addition and subtraction in two's complement notation can be performed by treating numbers

as if they are unsigned integers. True/ False

5. Instruction pipelining boosts performance but requires careful design for optimal results and

reasonable complexity. True/ False

6. Machine parallelism enables independent instructions to be executed simultaneously by

overlapping their execution. True/ False

7. Interrupt is one of the five states in a process's lifecycle. True/ False

8. RISC processors are more responsive to interrupts because interrupts are checked between

elementary operations. True/ False

9. Paging is typically visible to programmers and is used for organizing programs, data, and

managing privileges and protection attributes. True/ False

10. The XOR operator yields false if both operands are true. True/ False

11. It is not possible to connect 1/0 controllers directly to the system bus.True/ False

12. Organizational attributes consist of hardware details that are transparent to the programmer.

True/ False

13. In a system without virtual memory, the effective address is a virtual address or a register.

True/ False

14. Binary notation is more compact than hexadecimal notation. True/ False

15. AGP expansion cards found on the motherboard are superior to PCI Express (PCle).True / False

SECTION B (15 MARKS]: Each Question Weighs 1 Mark.

Choose the correct for each of the following:

1. In floating-point representation, what occurs when the significand cannot represent a number

due to insufficient bits?

A. Exponent overflow

B. Exponent underflow

C. Significand overflow

D. Significand underflow

Page 1 of 6

|

3 Page 3 |

▲back to top |

2. What operating system function manages the allocation of CPU time to different processes?

A. Memory management

B. Process scheduling

C. File system management

D. Device management

3. What is the base (or radix) of the hexadecimal number system?

A. 2

B. 8

C. 10

D. 16

4. In a binary number, what is the term for the rightmost digit?

A. Most significant digit

B. Least significant digit

C. Base digit

D. Radix digit

5. In which context is the precision of a fixed-point number format typically determined?

A. Hardware design

B. Software configuration

C. User input

D. Data transmission

6. Operating system controlWhich properties do all semiconductor memory cells share?

A. They exhibit two stable states which can be used to represent

B. Binary 1 and 0

C. They are capable of being written into to set the state

D. All of the above

7. A _ _ __ serves as the channel for communication between the CPU, main memory, and

input/output devices.

A. system interconnection B. CPU interconnection

C. peripheral

D. processor

8. The _ _ __ is responsible for determining both the opcode and the operand specifiers.

A. decode instruction

B. fetch operands

C. calculate operands

D. execute instruction

9. A ____ is a schedulable unit of work inside a process, complete with its own processor

context and stack data area.

A. Process

B. Process switch

C. Thread

D. Thread switch

Page 2 of6

|

4 Page 4 |

▲back to top |

10. The _ _ __ is the processor memory component that helps boost processor performance.

A.DDR3

B.DDR2

C. DDR4

D. Level 2 cache

11. Which of the follow ing statements best compares Amdahl's Law and Moore's Law in the context

of computer system performance improvement?

A. Amdahl's Law predicts the maximum improvement in computing speed by increasing

parallel processing, while Moore's Law observes the exponential growth in CPU clock

speed.

B. Amdahl's Law concerns the theoretical speedup from parallelization, w hereas Moore's

Law describes the doubl ing of transistors on integrated circuits approximately every

two years.

C. Both Amdahl's Law and Moore's Law are only applicable to hardware advancements and

do not affect software performance.

D. Amdah l's Law explains the increase in transistor density, while Moore's Law explains the

limits of parallel processing

12. Which of these interrelated factors are involved in dete rmining how add ressi ng bits are used?

A. number of operand s B. number of register sets

C. address range

D. all of the above

13. The simplest and most basic type of machine instruction is the _ _ _ _ instru ction.

A. conversion

B. data transfer

C. arithmetic

D. logica l

14. _ ___ are components in digital circuits that manage the routing of signals and data.

A. Multiplexers

B. Program counters

C. Flip-flops

D. Gates

15. A cache line contains a _ _ _ _ to indicate which specific block of data is currently stored.

A. cache

B. hit

C. tag

D. locality

Page 3 of6

|

5 Page 5 |

▲back to top |

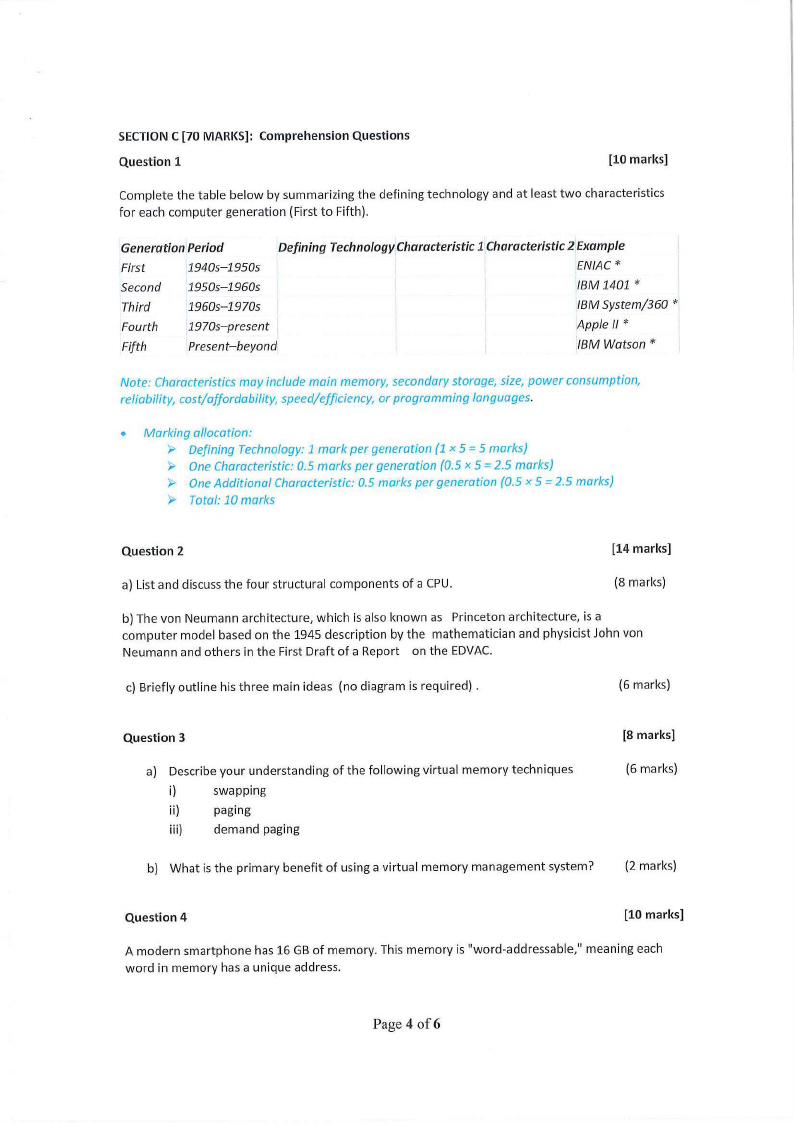

SECTION C [70 MARKS]: Comprehension Questions

Question 1

[10 marks]

Complete the table below by summarizing the defining technology and at least two characteristics

for each computer generation (First to Fifth).

Generation Period

Defining Technology Characteristic 1 Characteristic 2 Example

First

Second

Third

1940s-1950s

1950s-1960s

1960s-1970s

EN/AC *

IBM 1401 *

IBM System/360 *

Fourth 1970s-present

Apple fl*

Fifth

Present-beyond

IBM Watson *

Note: Chardcteristics may include main memory, secondary storage, size, power consumption,

reliability, cost/affordability, speed/efficiency, or programming languages.

• Marking a/location:

► Defining Technology: 1 mark per generation (1 x 5 = 5 marks)

► One Characteristic: 0.5 marks per generation (0.5 x 5 = 2.5 marks)

► One Additional Characteristic: 0.5 marks per generation (0.5 x 5 = 2.5 marks)

► Total: 10 marks

Question 2

[14 marks]

a) List and discuss the four structural components of a CPU.

(8 marks)

b) The van Neumann architecture, which is also known as Princeton architecture, is a

computer model based on the 1945 description by the mathematician and physicist John von

Neumann and others in the First Draft of a Report on the EDVAC.

c) Briefly outline his three main ideas (no diagram is required).

(6 marks)

Question 3

a) Describe your understanding of the following virtual memory techniques

i)

swapping

ii)

paging

iii)

demand paging

[8 marks]

(6 marks)

b) What is the primary benefit of using a virtual memory management system?

(2 marks)

Question 4

[10 marks]

A modern smartphone has 16 GB of memory. This memory is "word-addressable," meaning each

word in memory has a unique address.

Page 4 of 6

|

6 Page 6 |

▲back to top |

a) If each word in memory has its own address, how many total words can be stored in this

smartphone's memory? (Assume a standard word size of 4 bytes).

(4 marks)

b) Imagine this memory is organized into blocks, where each block holds 256 words. How many

blocks would the smartphone's memory have?

(3 marks)

c) If we use a "direct-mapped cache scheme," where each memory block is assigned to one specific

line in the cache, how many cache lines would be needed to hold all the blocks from part

(b)?

(3 marks)

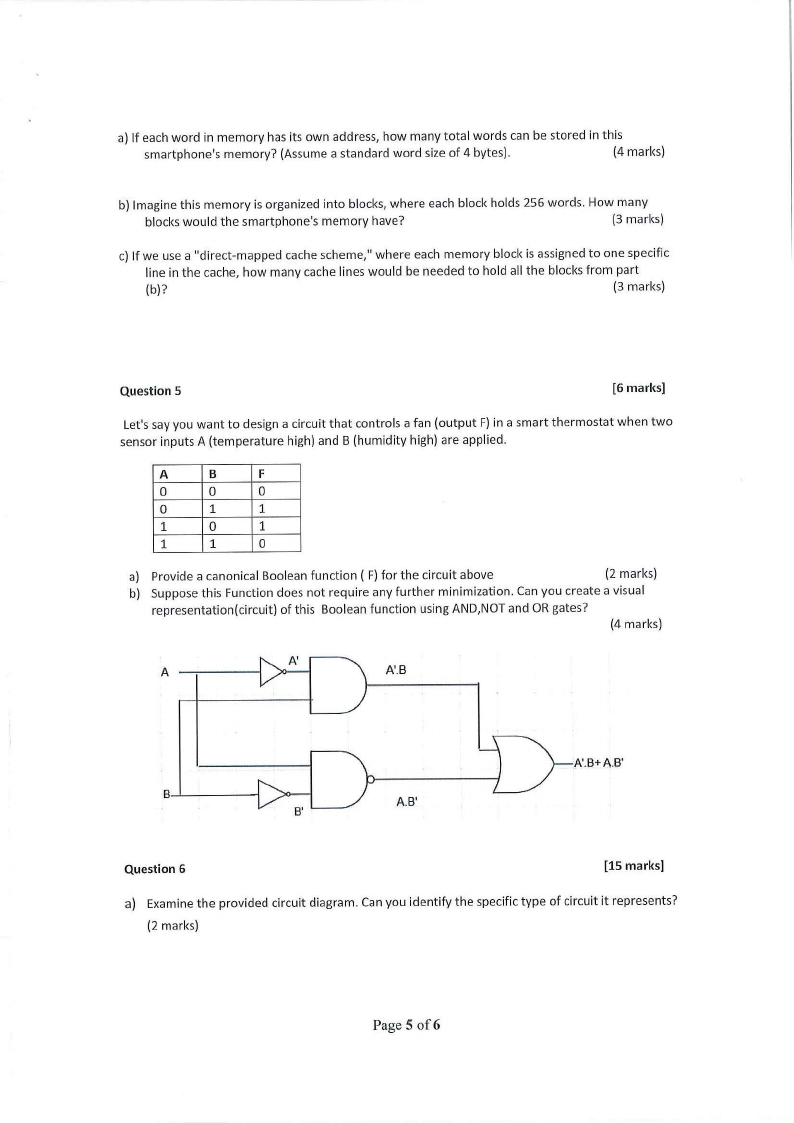

Question 5

[6 marks)

Let's say you want to design a circuit that controls a fan (output F) in a smart thermostat when two

sensor inputs A (temperature high) and B (humidity high) are applied.

A

B

F

0

0

0

0

1

1

1

0

1

1

1

0

a) Provide a canonical Boolean function ( F) for the circuit above

(2 marks)

b) Suppose this Function does not require any further minimization. Can you create a visual

representation(circuit) of this Boolean function using AND,NOT and OR gates?

(4 marks)

A

A'.B

B.....1------1

A.B'

A'.B+A.B'

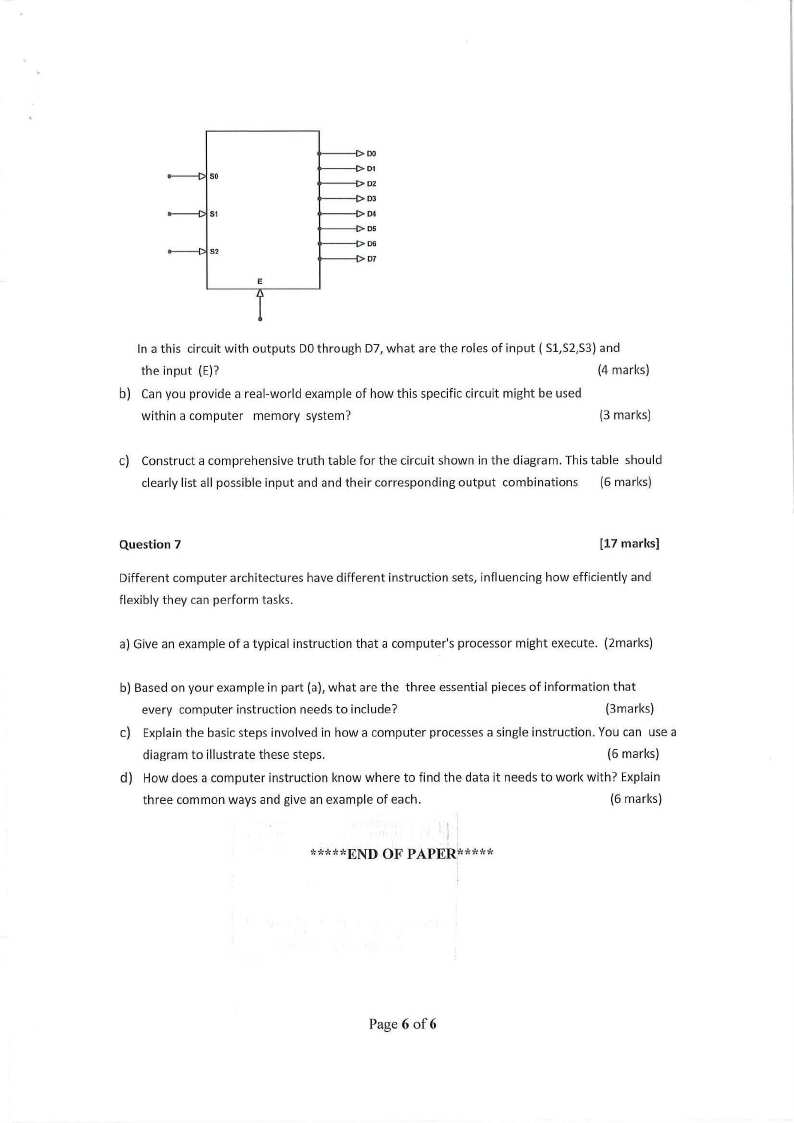

Question 6

[15 marks]

a) Examine the provided circuit diagram. Can you identify the specific type of circuit it represents?

(2 marks)

Page 5 of 6

|

7 Page 7 |

▲back to top |

_ _ _,.,DO

- - -1>D1

---h02

_ _ _,..,,03

- - -1> 04

- --1> D5

- - -r..os

- - -1> D7

E

In a this circuit with outputs DO through D7, what are the roles of input ( 51,52,53) and

the input (E)?

(4 marks)

b) Can you provide a real-world example of how this specific circuit might be used

within a computer memory system?

(3 marks)

c) Construct a comprehensive truth table for the circuit shown in the diagram. This table should

clearly list all possible input and and their corresponding output combinations (6 marks)

Question 7

[17 marks]

Different computer architectures have different instruction sets, influencing how efficiently and

flexibly they can perform tasks.

a) Give an example of a typical instruction that a computer's processor might execute. (2marks)

b) Based on your example in part (a), what are the three essential pieces of information that

every computer instruction needs to include?

(3marks)

c) Explain the basic steps involved in how a computer processes a single instruction. You can use a

diagram to illustrate these steps.

(6 marks)

d) How does a computer instruction know where to find the data it needs to work with? Explain

three common ways and give an example of each.

(6 marks)

I

*****END OF PAPER'**"d'*

Page 6 of 6